蝕刻與電子封裝界面的界面相容性研究主要涉及的是如何在蝕刻過(guò)程中保護(hù)電子封裝結(jié)構(gòu),,防止蝕刻劑侵入導(dǎo)致材料損傷或結(jié)構(gòu)失效的問(wèn)題。

首先,,需要考慮蝕刻劑的選擇,以確保其與電子封裝材料之間的相容性,。不同的材料對(duì)不同的蝕刻劑具有不同的抵抗能力,,因此需要選擇適合的蝕刻劑,以避免對(duì)電子封裝結(jié)構(gòu)造成損害,。

其次,,需要設(shè)計(jì)合適的蝕刻工藝參數(shù),以保護(hù)電子封裝結(jié)構(gòu),。這包括確定蝕刻劑的濃度,、蝕刻時(shí)間和溫度等參數(shù),,以確保蝕刻劑能夠在一定程度上去除目標(biāo)材料,同時(shí)盡量減少對(duì)電子封裝結(jié)構(gòu)的影響,。

此外,,還可以通過(guò)添加保護(hù)層或采用輔助保護(hù)措施來(lái)提高界面相容性。例如,,可以在電子封裝結(jié)構(gòu)表面涂覆一層保護(hù)膜,,以減少蝕刻劑對(duì)結(jié)構(gòu)的侵蝕。

在研究界面相容性時(shí),,還需要進(jìn)行一系列的實(shí)驗(yàn)和測(cè)試,,以評(píng)估蝕刻過(guò)程對(duì)電子封裝結(jié)構(gòu)的影響。這包括材料性能測(cè)試,、顯微鏡觀察,、電性能測(cè)試等。通過(guò)實(shí)驗(yàn)數(shù)據(jù)的分析和對(duì)結(jié)果的解釋?zhuān)梢赃M(jìn)一步優(yōu)化蝕刻工藝參數(shù),,以提高界面相容性,。

總的來(lái)說(shuō),蝕刻與電子封裝界面的界面相容性研究是一個(gè)復(fù)雜而細(xì)致的工作,,需要綜合考慮材料性質(zhì),、蝕刻劑選擇、工藝參數(shù)控制等多個(gè)因素,,以確保蝕刻過(guò)程中對(duì)電子封裝結(jié)構(gòu)的保護(hù)和保持其功能穩(wěn)定性,。蝕刻技術(shù):半導(dǎo)體封裝中的精密控制工藝!重慶無(wú)憂(yōu)半導(dǎo)體封裝載體

蝕刻技術(shù)作為一種重要的微米級(jí)加工技術(shù),,在半導(dǎo)體行業(yè)中有著廣泛的應(yīng)用。在半導(dǎo)體封裝載體制造中,,蝕刻技術(shù)有著多種應(yīng)用場(chǎng)景,。

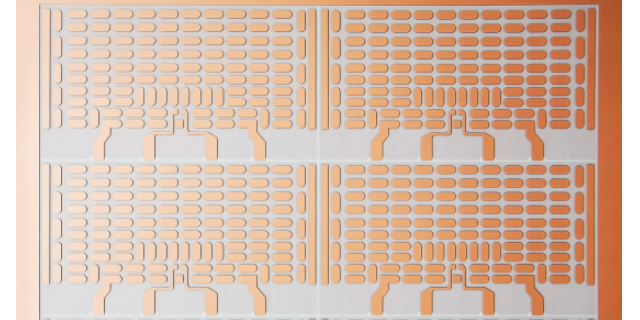

首先,蝕刻技術(shù)被用于刻蝕掉載體表面的金屬層,。在半導(dǎo)體封裝過(guò)程中,,載體表面通常需要背膜蝕刻,以去除金屬材料,,如銅或鎢,,從而減輕封裝模組的重量。蝕刻技術(shù)可以提供高度可控的蝕刻速率和均勻性,,保證金屬層被完全去除,,同時(shí)避免對(duì)其他部件造成損害。

其次,,蝕刻技術(shù)還可以用來(lái)制備載體表面的微細(xì)結(jié)構(gòu),。在一些特殊的封裝載體中,,比如MEMS,需要通過(guò)蝕刻技術(shù)在載體表面制造出微觀結(jié)構(gòu),,如微凹陷或槽口,,以實(shí)現(xiàn)特定的功能。蝕刻技術(shù)可以在不同材料上實(shí)現(xiàn)高分辨率的微細(xì)結(jié)構(gòu)加工,,滿(mǎn)足不同尺寸和形狀的需求,。

此外,蝕刻技術(shù)還被廣泛應(yīng)用于載體表面的清洗和處理,。在半導(dǎo)體封裝過(guò)程中,,載體表面需要經(jīng)過(guò)清洗和處理,以去除雜質(zhì),、保證良好的黏附性和界面質(zhì)量,。蝕刻技術(shù)可以通過(guò)選擇適當(dāng)?shù)奈g刻溶液和蝕刻條件,實(shí)現(xiàn)對(duì)載體表面的清洗和活化處理,,提高后續(xù)工藝步驟的成功率,。

總之,蝕刻技術(shù)在半導(dǎo)體封裝載體制造中具有重要的應(yīng)用價(jià)值,。它可以用于去除金屬層,、制備微細(xì)結(jié)構(gòu)以及清洗和處理載體表面,從而為封裝過(guò)程提供更好的品質(zhì)和效率,。甘肅半導(dǎo)體封裝載體金屬蝕刻技術(shù)對(duì)于半導(dǎo)體封裝的性能和穩(wěn)定性的提升,!

高密度半導(dǎo)體封裝載體的研究與設(shè)計(jì)是指在半導(dǎo)體封裝領(lǐng)域,針對(duì)高密度集成電路的應(yīng)用需求,,設(shè)計(jì)和研發(fā)適用于高密度封裝的封裝載體,。以下是高密度半導(dǎo)體封裝載體研究與設(shè)計(jì)的關(guān)鍵點(diǎn):

1. 器件布局和連接設(shè)計(jì):在有限封裝空間中,優(yōu)化器件的布局和互聯(lián)結(jié)構(gòu),,以實(shí)現(xiàn)高密度封裝,。采用新的技術(shù)路線,如2.5D和3D封裝,,可以進(jìn)一步提高器件集成度,。

2. 連接技術(shù):選擇和研發(fā)適合高密度封裝的連接技術(shù),如焊接,、焊球,、微小管等,以實(shí)現(xiàn)高可靠性和良好的電氣連接性,。

3. 封裝材料和工藝:選擇適合高密度封裝的先進(jìn)封裝材料,如高導(dǎo)熱材料,、低介電常數(shù)材料等,,以提高散熱性能和信號(hào)傳輸能力,。

4. 工藝控制和模擬仿真:通過(guò)精確的工藝控制和模擬仿真,優(yōu)化封裝過(guò)程中的參數(shù)和工藝條件,,確保高密度封裝器件的穩(wěn)定性和可靠性,。

5. 可靠性測(cè)試和驗(yàn)證:對(duì)設(shè)計(jì)的高密度封裝載體進(jìn)行可靠性測(cè)試,評(píng)估其在不同工作條件下的性能和壽命,。

高密度半導(dǎo)體封裝載體的研究與設(shè)計(jì),,對(duì)于滿(mǎn)足日益增長(zhǎng)的電子產(chǎn)品對(duì)小尺寸、高性能的需求至關(guān)重要,。需要綜合考慮器件布局,、連接技術(shù)、封裝材料和工藝等因素,,進(jìn)行優(yōu)化設(shè)計(jì),,以提高器件的集成度和性能,同時(shí)確保封裝載體的穩(wěn)定性和可靠性,。

探索蝕刻在半導(dǎo)體封裝中的3D封裝組裝技術(shù)研究,,主要關(guān)注如何利用蝕刻技術(shù)實(shí)現(xiàn)半導(dǎo)體封裝中的三維(3D)封裝組裝。

首先,,需要研究蝕刻技術(shù)在3D封裝組裝中的應(yīng)用,。蝕刻技術(shù)可以用于去除封裝結(jié)構(gòu)之間的不需要的材料或?qū)樱詫?shí)現(xiàn)封裝組件的3D組裝,??梢钥紤]使用濕蝕刻或干蝕刻,根據(jù)具體的組裝需求選擇合適的蝕刻方法,。

其次,,需要考慮蝕刻對(duì)封裝結(jié)構(gòu)的影響。蝕刻過(guò)程可能會(huì)對(duì)封裝結(jié)構(gòu)造成損傷,,如產(chǎn)生裂紋,、改變尺寸和形狀等。因此,,需要評(píng)估蝕刻工藝對(duì)封裝結(jié)構(gòu)的影響,,以減少潛在的失效風(fēng)險(xiǎn)。

此外,,需要研究蝕刻工藝的優(yōu)化和控制,。蝕刻工藝參數(shù)的選擇和控制對(duì)于實(shí)現(xiàn)高質(zhì)量的3D封裝組裝非常重要。需要考慮蝕刻劑的選擇,、濃度,、溫度、蝕刻時(shí)間等參數(shù),并通過(guò)實(shí)驗(yàn)和優(yōu)化算法等手段,,找到適合的蝕刻工藝條件,。

在研究3D封裝組裝中的蝕刻技術(shù)時(shí),還需要考慮蝕刻過(guò)程的可重復(fù)性和一致性,。確保蝕刻過(guò)程在不同的批次和條件下能夠產(chǎn)生一致的結(jié)果,,以便實(shí)現(xiàn)高效的生產(chǎn)和組裝。綜上所述,,蝕刻在半導(dǎo)體封裝中的3D封裝組裝技術(shù)研究需要綜合考慮蝕刻技術(shù)的應(yīng)用,、對(duì)封裝結(jié)構(gòu)的影響、蝕刻工藝的優(yōu)化和控制等多個(gè)方面,。通過(guò)實(shí)驗(yàn),、數(shù)值模擬和優(yōu)化算法等手段,可以實(shí)現(xiàn)高質(zhì)量和可靠性的3D封裝組裝,??刂瓢雽?dǎo)體封裝技術(shù)中的熱和電磁干擾。

在三維封裝中,,半導(dǎo)體封裝載體的架構(gòu)優(yōu)化研究主要關(guān)注如何提高封裝載體的性能,、可靠性和制造效率,以滿(mǎn)足日益增長(zhǎng)的電子產(chǎn)品對(duì)高密度封裝和高可靠性的需求,。

1. 材料選擇和布局優(yōu)化:半導(dǎo)體封裝載體通常由有機(jī)基板或無(wú)機(jī)材料制成,。優(yōu)化材料選擇及其在載體上的布局可以提高載體的熱導(dǎo)率、穩(wěn)定性和耐久性,。

2. 電氣和熱傳導(dǎo)優(yōu)化:對(duì)于三維封裝中的多個(gè)芯片堆疊,,優(yōu)化電氣和熱傳導(dǎo)路徑可以提高整個(gè)封裝系統(tǒng)的性能。通過(guò)設(shè)計(jì)導(dǎo)熱通道和優(yōu)化電路布線,,可以降低芯片溫度,、提高信號(hào)傳輸速率和降低功耗。

3. 結(jié)構(gòu)強(qiáng)度和可靠性?xún)?yōu)化:三維封裝中的芯片堆疊會(huì)產(chǎn)生較大的應(yīng)力和振動(dòng),,因此,,優(yōu)化載體的結(jié)構(gòu)設(shè)計(jì),提高結(jié)構(gòu)強(qiáng)度和可靠性是非常重要的,。

4. 制造工藝優(yōu)化:對(duì)于三維封裝中的半導(dǎo)體封裝載體,,制造工藝的優(yōu)化可以提高制造效率和降低成本。例如,,采用先進(jìn)的制造工藝,,如光刻、薄在進(jìn)行三維封裝時(shí),,半導(dǎo)體封裝載體扮演著重要的角色,,對(duì)于架構(gòu)的優(yōu)化研究可以提高封裝的性能和可靠性,。

這些研究方向可以從不同角度對(duì)半導(dǎo)體封裝載體的架構(gòu)進(jìn)行優(yōu)化,提高封裝的性能和可靠性,,滿(mǎn)足未來(lái)高性能和高集成度的半導(dǎo)體器件需求,。蝕刻技術(shù)對(duì)于半導(dǎo)體封裝的材料選擇的重要性!重慶無(wú)憂(yōu)半導(dǎo)體封裝載體

蝕刻技術(shù)如何實(shí)現(xiàn)半導(dǎo)體封裝中的尺寸縮?。≈貞c無(wú)憂(yōu)半導(dǎo)體封裝載體

蝕刻作為一種常用的加工技術(shù),,對(duì)半導(dǎo)體封裝載體表面粗糙度有著較大的影響,。載體表面粗糙度是指載體表面的不平整程度,它對(duì)于器件封裝的質(zhì)量和性能起著重要的影響,。

首先,,蝕刻過(guò)程中的蝕刻副產(chǎn)物可能會(huì)引起載體表面的粗糙度增加。蝕刻副產(chǎn)物主要是由于蝕刻溶液中的化學(xué)反應(yīng)產(chǎn)生的,,它們?cè)诒砻娉练e形成蝕刻剩余物,。這些剩余物會(huì)導(dǎo)致載體表面的粗糙度增加,影響后續(xù)封裝工藝的可靠性和一致性,。

其次,,蝕刻速率的控制也會(huì)對(duì)載體表面粗糙度產(chǎn)生影響。蝕刻速率是指在單位時(shí)間內(nèi)材料被移除的厚度,。如果蝕刻速率過(guò)快,,會(huì)導(dǎo)致載體表面的不均勻性和粗糙度增加。因此,,通過(guò)調(diào)整蝕刻參數(shù),,如蝕刻溶液的成分和濃度、溫度和壓力等,,可以控制蝕刻速率,,實(shí)現(xiàn)對(duì)載體表面粗糙度的優(yōu)化。

此外,,蝕刻前后的表面處理也是優(yōu)化載體表面粗糙度的重要策略,。表面處理可以包括清洗、活化等步驟,,它們可以去除表面的污染和氧化物,,并提高蝕刻后的表面質(zhì)量。適當(dāng)?shù)谋砻嫣幚砟軌驕p小載體表面粗糙度,,提高封裝工藝的成功率,。

總結(jié)起來(lái),蝕刻對(duì)半導(dǎo)體封裝載體表面粗糙度有著較大的影響,。為了優(yōu)化載體表面粗糙度,,我們可以采取控制蝕刻副產(chǎn)物的形成與去除,、調(diào)整蝕刻速率以及進(jìn)行適當(dāng)?shù)谋砻嫣幚淼炔呗浴V貞c無(wú)憂(yōu)半導(dǎo)體封裝載體