蝕刻技術(shù)在半導(dǎo)體封裝中的后續(xù)工藝優(yōu)化研究主要關(guān)注如何優(yōu)化蝕刻工藝,以提高封裝的制造質(zhì)量和性能,。

首先,,需要研究蝕刻過程中的工藝參數(shù)對(duì)封裝質(zhì)量的影響。蝕刻劑的濃度,、溫度,、蝕刻時(shí)間等參數(shù)都會(huì)對(duì)封裝質(zhì)量產(chǎn)生影響,如材料去除速率,、表面粗糙度,、尺寸控制等。

其次,,需要考慮蝕刻過程對(duì)封裝材料性能的影響,。蝕刻過程中的化學(xué)溶液或蝕刻劑可能會(huì)對(duì)封裝材料產(chǎn)生損傷或腐蝕,影響封裝的可靠性和壽命,??梢赃x擇適合的蝕刻劑、優(yōu)化蝕刻工藝參數(shù),以減少材料損傷,。

此外,,還可以研究蝕刻后的封裝材料表面處理技術(shù)。蝕刻后的封裝材料表面可能存在粗糙度,、異物等問題,,影響封裝的光學(xué)、電學(xué)或熱學(xué)性能,。研究表面處理技術(shù),,如拋光、蝕刻劑殘留物清潔,、表面涂層等,,可以改善封裝材料表面的質(zhì)量和光學(xué)性能。

在研究蝕刻技術(shù)的后續(xù)工藝優(yōu)化時(shí),,還需要考慮制造過程中的可重復(fù)性和一致性,。需要確保蝕刻過程在不同的批次和條件下能夠產(chǎn)生一致的結(jié)果,以提高封裝制造的效率和穩(wěn)定性,。

總之,,蝕刻技術(shù)在半導(dǎo)體封裝中的后續(xù)工藝優(yōu)化研究需要綜合考慮蝕刻工藝參數(shù)、對(duì)材料性質(zhì)的影響,、表面處理技術(shù)等多個(gè)方面,。通過實(shí)驗(yàn)、優(yōu)化算法和制造工藝控制等手段,,實(shí)現(xiàn)高質(zhì)量,、可靠性和一致性的封裝制造。蝕刻技術(shù):半導(dǎo)體封裝中的精密控制工藝,!山東半導(dǎo)體封裝載體金屬

蝕刻技術(shù)在半導(dǎo)體封裝中用于調(diào)控微觀結(jié)構(gòu)是非常重要的,。下面是一些常用的微觀結(jié)構(gòu)調(diào)控方法:

蝕刻選擇性:蝕刻選擇性是指在蝕刻過程中選擇性地去除特定的材料。通過調(diào)整蝕刻液的成分,、濃度,、溫度和時(shí)間等參數(shù),可以實(shí)現(xiàn)對(duì)特定材料的選擇性蝕刻,。這樣可以在半導(dǎo)體封裝中實(shí)現(xiàn)微觀結(jié)構(gòu)的調(diào)控,,如開孔、通孔和刻蝕坑等,。

掩模技術(shù):掩模技術(shù)是通過在待蝕刻的表面上覆蓋一層掩膜或掩膜圖案來控制蝕刻區(qū)域,。掩膜可以是光刻膠、金屬膜或其他材料,。通過光刻工藝制備精細(xì)的掩膜圖案,,可以實(shí)現(xiàn)對(duì)微觀結(jié)構(gòu)的精確定位和形狀控制,。

物理輔助蝕刻技術(shù):物理輔助蝕刻技術(shù)是指在蝕刻過程中通過物理機(jī)制來輔助蝕刻過程,從而實(shí)現(xiàn)微觀結(jié)構(gòu)的調(diào)控,。例如,,通過施加外加電場(chǎng)、磁場(chǎng)或機(jī)械力,,可以改變蝕刻動(dòng)力學(xué),,達(dá)到所需的結(jié)構(gòu)調(diào)控效果。

溫度控制:蝕刻過程中的溫度控制也是微觀結(jié)構(gòu)調(diào)控的重要因素,。通過調(diào)整蝕刻液的溫度,,可以影響蝕刻動(dòng)力學(xué)和表面反應(yīng)速率,從而實(shí)現(xiàn)微觀結(jié)構(gòu)的調(diào)控,。

需要注意的是,,在進(jìn)行微觀結(jié)構(gòu)調(diào)控時(shí),需要綜合考慮多種因素,,如蝕刻液的成分和濃度,、蝕刻時(shí)間、溫度,、壓力等。同時(shí),,還需要對(duì)蝕刻過程進(jìn)行嚴(yán)密的控制和監(jiān)測(cè),,以確保所得到的微觀結(jié)構(gòu)符合預(yù)期要求。山東半導(dǎo)體封裝載體功能蝕刻技術(shù)如何實(shí)現(xiàn)半導(dǎo)體封裝中的高密度布線,!

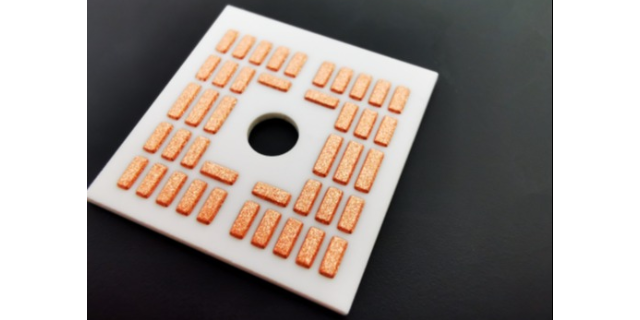

半導(dǎo)體封裝載體的材料選擇和優(yōu)化研究是一個(gè)關(guān)鍵的領(lǐng)域,,對(duì)提升半導(dǎo)體封裝技術(shù)的性能和可靠性至關(guān)重要。我們生產(chǎn)時(shí)著重從這幾個(gè)重要的方面考慮:

熱性能:半導(dǎo)體封裝載體需要具有良好的熱傳導(dǎo)性能,,以有效地將熱量從芯片散熱出去,,防止芯片溫度過高而導(dǎo)致性能下降或失效。

電性能:半導(dǎo)體封裝載體需要具有良好的電絕緣性能,,以避免電流泄漏或短路等電性問題,。對(duì)于一些高頻應(yīng)用,材料的介電常數(shù)也是一個(gè)重要考慮因素,,較低的介電常數(shù)可以減少信號(hào)傳輸?shù)膿p耗,。

機(jī)械性能:半導(dǎo)體封裝載體需要具有足夠的機(jī)械強(qiáng)度和剛性,以保護(hù)封裝的芯片免受外界的振動(dòng),、沖擊和應(yīng)力等,。此外,材料的疲勞性能和形變能力也需要考慮,,以便在不同溫度和應(yīng)力條件下保持結(jié)構(gòu)的完整性,。

可制造性:材料的可制造性是另一個(gè)重要方面,,包括材料成本、可用性,、加工和封裝工藝的兼容性等,。考慮到效益和可持續(xù)發(fā)展的要求,,環(huán)境友好性也是需要考慮的因素之一,。

其他特殊要求:根據(jù)具體的應(yīng)用場(chǎng)景和要求,可能還需要考慮一些特殊的材料性能,,如耐腐蝕性,、抗射線輻射性、阻燃性等,。通過綜合考慮以上因素,,可以選擇和優(yōu)化適合特定應(yīng)用的半導(dǎo)體封裝載體材料,以提高封裝技術(shù)的性能,、可靠性和可制造性,。

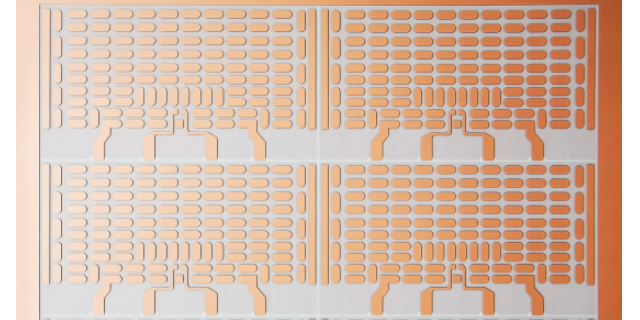

基于蝕刻技術(shù)的高密度半導(dǎo)體封裝器件設(shè)計(jì)與優(yōu)化涉及到以下幾個(gè)方面:

1. 設(shè)計(jì):首先需要進(jìn)行器件的設(shè)計(jì),包括電路布局,、層次結(jié)構(gòu)和尺寸等,。設(shè)計(jì)過程中考慮到高密度封裝的要求,需要盡量減小器件尺寸,,提高器件的集成度,。

2. 材料選擇:選擇合適的材料對(duì)器件性能至關(guān)重要。需要考慮材料的導(dǎo)電性,、導(dǎo)熱性,、抗腐蝕性等性能,以及與蝕刻工藝的配合情況,。

3. 蝕刻工藝:蝕刻技術(shù)是半導(dǎo)體器件制備過程中的關(guān)鍵步驟,。需要選擇合適的蝕刻劑和工藝參數(shù),使得器件的圖案能夠得到良好的加工,。

4. 優(yōu)化:通過模擬和實(shí)驗(yàn),,對(duì)設(shè)計(jì)的器件進(jìn)行優(yōu)化,以使其性能達(dá)到較好狀態(tài),。優(yōu)化的主要目標(biāo)包括減小電阻,、提高導(dǎo)電性和降低功耗等。

5. 封裝和測(cè)試:設(shè)計(jì)和優(yōu)化完成后,,需要對(duì)器件進(jìn)行封裝和測(cè)試,。封裝工藝需要考慮器件的密封性和散熱性,以保證器件的可靠性和工作穩(wěn)定性,。

總的來說,,基于蝕刻技術(shù)的高密度半導(dǎo)體封裝器件設(shè)計(jì)與優(yōu)化需要綜合考慮器件設(shè)計(jì),、材料選擇、蝕刻工藝,、優(yōu)化和封裝等方面的問題,,以達(dá)到高集成度、高性能和高可靠性的要求,。蝕刻技術(shù)如何實(shí)現(xiàn)半導(dǎo)體封裝中的電路互聯(lián),!

蝕刻工藝在半導(dǎo)體封裝器件中對(duì)光學(xué)性能進(jìn)行優(yōu)化的研究是非常重要的。下面是一些常見的研究方向和方法:

1. 光學(xué)材料選擇:選擇合適的光學(xué)材料是優(yōu)化光學(xué)性能的關(guān)鍵,。通過研究和選擇具有良好光學(xué)性能的材料,,如高透明度、低折射率和低散射率的材料,,可以改善封裝器件的光學(xué)特性,。

2. 去除表面缺陷:蝕刻工藝可以用于去除半導(dǎo)體封裝器件表面的缺陷和污染物,從而減少光的散射和吸收,。通過優(yōu)化蝕刻參數(shù),,如蝕刻液的濃度、溫度和蝕刻時(shí)間等,,可以實(shí)現(xiàn)對(duì)表面缺陷的清潔,,提高光學(xué)性能。

3. 調(diào)控表面形貌:通過蝕刻工藝中的選擇性蝕刻,、掩模技術(shù)和物理輔助蝕刻等方法,,可以控制封裝器件的表面形貌,如設(shè)計(jì)微結(jié)構(gòu),、改變表面粗糙度等。這些調(diào)控方法可以改變光在器件表面的傳播和反射特性,,從而優(yōu)化光學(xué)性能,。

4. 光學(xué)層的制備:蝕刻工藝可以用于制備光學(xué)層,如反射層,、濾光層和抗反射層,。通過優(yōu)化蝕刻參數(shù)和材料選擇,可以實(shí)現(xiàn)光學(xué)層的精確控制,,從而提高封裝器件的光學(xué)性能,。

5. 光學(xué)模擬與優(yōu)化:使用光學(xué)模擬軟件進(jìn)行系統(tǒng)的光學(xué)仿真和優(yōu)化,可以預(yù)測(cè)和評(píng)估不同蝕刻工藝對(duì)光學(xué)性能的影響,。通過優(yōu)化蝕刻參數(shù),,可以選擇適合的工藝方案,從而實(shí)現(xiàn)光學(xué)性能的優(yōu)化,。蝕刻技術(shù):半導(dǎo)體封裝中的精細(xì)加工利器,!江西半導(dǎo)體封裝載體歡迎選購

蝕刻技術(shù)如何實(shí)現(xiàn)半導(dǎo)體封裝中的微米級(jí)加工,!山東半導(dǎo)體封裝載體金屬

半導(dǎo)體封裝載體中的信號(hào)傳輸與電磁兼容性研究是指在半導(dǎo)體封裝過程中,針對(duì)信號(hào)傳輸和電磁兼容性的需求,,研究如何優(yōu)化信號(hào)傳輸和降低電磁干擾,,確保封裝器件的可靠性和穩(wěn)定性。

1. 信號(hào)傳輸優(yōu)化:分析信號(hào)傳輸路徑和布線,,優(yōu)化信號(hào)線的走向,、布局和長(zhǎng)度,以降低信號(hào)傳輸中的功率損耗和信號(hào)失真,。

2. 電磁兼容性設(shè)計(jì):設(shè)計(jì)和優(yōu)化封裝載體的結(jié)構(gòu)和屏蔽,,以減少或屏蔽電磁輻射和敏感性。采用屏蔽罩,、屏蔽材料等技術(shù)手段,,提高封裝器件的電磁兼容性。

3. 電磁干擾抑制技術(shù):研究和應(yīng)用抑制電磁干擾的技術(shù),,如濾波器,、隔離器、電磁屏蔽等,,降低封裝載體內(nèi)外電磁干擾的影響,。通過優(yōu)化封裝結(jié)構(gòu)和設(shè)計(jì),提高器件的抗干擾能力,。

4. 模擬仿真與測(cè)試:利用模擬仿真工具進(jìn)行信號(hào)傳輸和電磁兼容性的模擬設(shè)計(jì)與分析,,評(píng)估封裝載體的性能。進(jìn)行實(shí)驗(yàn)室測(cè)試和驗(yàn)證,,確保設(shè)計(jì)的有效性和可靠性,。

需要綜合考慮信號(hào)傳輸優(yōu)化、電磁兼容性設(shè)計(jì),、電磁干擾抑制技術(shù),、模擬仿真與測(cè)試、標(biāo)準(zhǔn)遵循與認(rèn)證等方面,,進(jìn)行系統(tǒng)設(shè)計(jì)和優(yōu)化,,以提高封裝載體的抗干擾能力和電磁兼容性,確保信號(hào)的傳輸質(zhì)量和器件的穩(wěn)定性,。山東半導(dǎo)體封裝載體金屬